| INPUT A B | OUTPUT A + B | |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

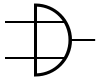

Ada tiga simbol untuk gerbang OR: Amerika (ANSI atau 'militer') simbol dan IEC('Eropa' atau 'persegi panjang') simbol, serta simbol DIN usang. Untuk informasilebih lanjut lihat Simbol Gerbang Logika.

|  |  |

| MIL/ANSI Symbol | IEC Symbol | DIN Symbol |

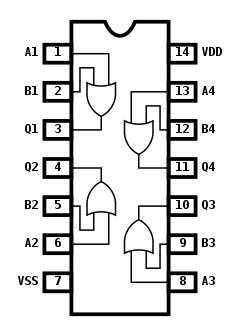

OR Gates gerbang logika dasar, dan karena itu mereka tersedia dalam keluargalogika TTL dan CMOS IC. Para seri 4000 standar IC CMOS adalah 4071, yang mencakup empat independen dua input gerbang OR. Versi TTL tradisional adalah7432. Ada banyak cabang 7432 asli gerbang OR. Semua memiliki pinout yang sama tetapi arsitektur internal yang berbeda, yang memungkinkan mereka untuk beroperasi di rentang tegangan yang berbeda dan / atau pada kecepatan lebih tinggi. Selain Input 2-standar ATAU Gerbang, 3 - dan 4-input OR Gates juga tersedia. Dalam seri CMOS, ini adalah:

4075: Triple 3-input gerbang OR

4072: Dual 4-input gerbang OR

TTL variasi meliputi:

74LS32: Quad 2-input gerbang OR (versi Schottky daya rendah)

74HC32: Quad 2-input gerbang OR (High Speed CMOS versi) - memiliki konsumsiarus yang lebih rendah / jangkauan yang lebih luas Tegangan

74LVC32: tegangan rendah versi CMOS yang sama.

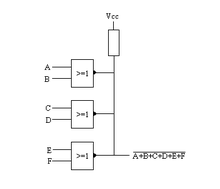

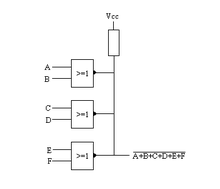

Jika tidak ada yang spesifik gerbang OR yang tersedia, satu dapat dibuat darigerbang NAND dalam konfigurasi ditunjukkan di bawah ini. Setiap gerbang logikadapat dibuat dari kombinasi gerbang NAND

Jika tidak ada yang spesifik gerbang OR yang tersedia, satu dapat dibuat darigerbang NAND dalam konfigurasi ditunjukkan di bawah ini. Setiap gerbang logikadapat dibuat dari kombinasi gerbang NAND

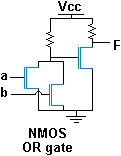

Dengan aktif rendah open-kolektor output logika, seperti yang digunakan untuk sinyal-sinyal kontrol dalam banyak sirkuit, sebuah fungsi OR dapat diproduksi oleh kabel bersama-sama beberapa output. Susunan ini disebut kabel OR. Iniimplementasi dari fungsi OR biasanya juga ditemukan dalam sirkuit terpadu N atau P-jenis transistor proses saja.

Tidak ada komentar:

Posting Komentar